发布时间:2024-12-19

发布时间:2024-12-19 点击次数:

点击次数: (文/Oliver),芯片行业的资本和技术壁垒都比较高,巨额的研发成本需要有足够大的市场来进行匹配。对于芯片厂商来说,除了要有软硬件技术开发的基本实力,还要能够洞察市场和控制成本。

AI芯片在过去两年中炙手可热,各路芯片巨头铆足劲比拼产品的峰值算力,制造工艺也在不断下探。而在这激烈的竞争之下,芯片厂商“无暇顾及”市场对于算力性价比的需求。

iResearch报告指出,英伟达基于其完备的GPU+CUDA生态主导云端AI芯片市场,但其产品售价高昂,GPU计算效能及功耗不如FPGA和ASIC芯片,市场渴望寻求替代方案。对此,初创AI芯片公司鲲云科技的联合创始人牛昕宇博士表示:“超越英伟达的一定不会是另一款GPU。”

牛博士表示,做AI芯片有两条路,一条是跟随着去做指令集架构,比拼峰值算力、工艺和外部带宽。但指令集架构很难在芯片利用率上拉开差距,而且英伟达已经在这条路上遥遥领先;而另一条路就是做数据流AI芯片,追求芯片利用率,用已有的芯片提供更高的性能,而鲲云科技已经打通了这条路。

近日,鲲云科技发布了全球首款数据流AI芯片CAISA,定位于高性能AI推理,目前已完成量产。第三方测试数据显示,仅用1/3的峰值算力,CAISA芯片可以实现英伟达T4最高3.91倍的实测性能。

CAISA芯片的实测算力远超英伟达T4,但峰值算力却比T4要低。牛博士表示,AI芯片的峰值算力并不是实测算力,峰值算力是一个理论化、学术化的数值,因为它需要这颗芯片中所有的计算单元每时每刻每一个时钟周期都在工作。在实际应用中,峰值算力还需要乘以一个系数——芯片利用率。

牛博士指出,当提供一样的实测算力时,峰值算力越高,意味着成本越高。这正好给了AI芯片一个新的机会,如果能将原本只有7%的芯片利用率提高到70%甚至是90%,就能够免费为用户提供10倍的算力提升。鲲云科技将这个机会发挥到了极致,CAISA的芯片利用率高达95.4%。

为何一些厂商最新的、最旗舰的、最领先的技术无法提供高芯片利用率呢?牛博士表示,芯片利用率只与芯片的架构有关,AI芯片主流的指令集架构背后是冯诺伊曼计算体系,其计算和控制是分离的,任何指令的组合方式都可以支持。虽然通用性很强,但该架构当前指令一定要在前一个指令之后执行才能保证计算的正确性。而前一个指令的完成时间存在不确定性,因此只能耗费时间等待。

指令集架构需要花费大量的时间来等待指令的到来,这给芯片利用率设置了一个很低的天花板,而数据流的计算方式则能够很好地打破这个天花板。

牛博士举例表示,指令集架构要求加法一定要在乘法后面来执行,这需要耗费等待时间。而数据流的计算方式能够让数据在这个流水线中永远是保证先流过乘法,再流过加法,进而把指令的等待周期消除。简言之,数据流架构是数据传输和计算每时每刻都在并行进行。

据介绍,此次发布的CAISA芯片采用鲲云自研的定制数据流芯片架构CAISA 3.0,相较于上一代芯片架构,CAISA3.0在架构效率和实测性能方面有了大幅的提升,并在算子支持上更加通用,支持绝大多数神经网络模型快速实现检测、分类和语义分割部署。CAISA3.0在多引擎支持上提供了4倍更高的并行度选择,架构的可拓展性大大提高,在AI芯片内,每一个CAISA都可以同时处理AI工作负载,进一步提升了CAISA架构的性能,在峰值算力提升6倍的同时保持了高达95.4%的芯片利用率,实测性能线性提升。同时新一代CAISA架构对编译器RainBuilder的支持更加友好,软硬件协作进一步优化,在系统级别上为用户提供更好的端到端性能。

CAISA3.0架构继续保持在数据流技术路线的全球领先地位,指令集架构采用冯诺依曼计算方式,通过指令执行次序控制计算顺序,并通过分离数据搬运与数据计算提供计算通用性。CAISA架构依托数据流流动次序控制计算次序,采用计算流和数据流重叠运行方式消除空闲计算单元,并采用动态配置方式保证对于人工智能算法的通用支持,突破指令集技术对于芯片算力的限制。此次升级,CAISA架构解决了数据流架构作为人工智能计算平台的三大核心挑战:

1.高算力性价比:在保持计算正确前提下,通过不断压缩每个空闲时钟推高芯片实测性能以接近芯片物理极限,让芯片内的每个时钟、每个计算单元都在执行有效计算;

2.高架构通用性:在保证每个算法在CAISA上运行能够实现高芯片利用率的同时,CAISA3.0架构通用支持所有主流CNN算法;

3.高软件易用性:通过专为CAISA定制的编译工具链实现算法端到端自动部署,用户无需底层数据流架构背景知识,简单两步即可实现算法迁移和部署,降低使用门槛。

具体来讲,鲲云CAISA3.0架构的三大技术突破主要通过以下的技术方式实现:

CAISA3.0架构由数据流来驱动计算过程,无指令操作,可以实现时钟级准确的计算,最大限度的减少硬件计算资源的空闲时间。CAISA3.0架构通过数据计算与数据流动的重叠,压缩计算资源的每一个空闲时钟;通过算力资源的动态平衡,消除流水线的性能瓶颈;通过数据流的时空映射,最大化复用芯片内的数据流带宽,减少对外部存储带宽的需求。上述设计使CNN算法的计算数据在CAISA3.0内可以实现不间断的持续运算,最高可实现95.4%的芯片利用率,在同等峰值算力条件下,可获得相对于GPU 3倍以上的实测算力,从而为用户提供更高的算力性价比。

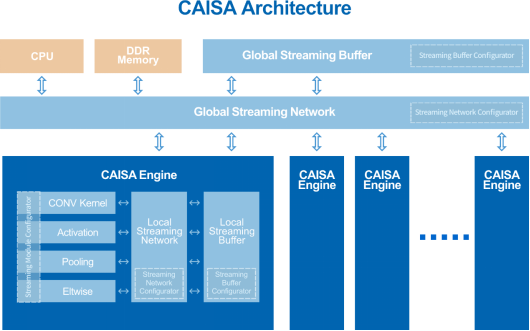

CAISA3.0架构可以通过流水线动态重组实现对不同深度学习算法的高性能支持。通过CAISA架构层的数据流引擎、全局数据流网、全局数据流缓存,以及数据流引擎内部的人工智能算子模块、局部数据流网、局部数据流缓存的分层设计,在数据流配置器控制下,CAISA架构中的数据流连接关系和运行状态都可以被自动化动态配置,从而生成面向不同AI算法的高性能定制化流水线。在保证高性能的前提下,支持用户使用基于CAISA3.0架构的计算平台实现如目标检测、分类及语义分割等广泛的人工智能算法应用。

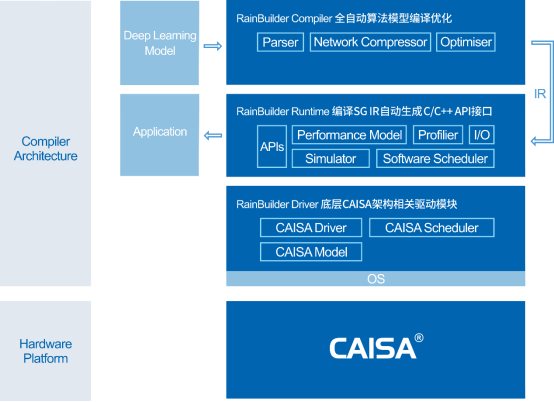

专为CAISA3.0架构配备的RainBuilder编译工具链支持从算法到芯片的端到端自动化部署,用户和开发者无需了解架构的底层硬件配置,简单两步即可实现算法快速迁移和部署。RainBuilder编译器可自动提取主流AI开发框架(TensorFlow,Caffe,Pytorch,ONNX等)中开发的深度学习算法的网络结构和参数信息,并面向CAISA结构进行优化;工具链中的运行时(Runtime)和驱动(Driver)模块负责硬件管理并为用户提供标准的API接口,运行时可以基于精确的CAISA性能模型,实现算法向CAISA架构的自动化映射,同时提供可以被高级语言直接调用的API接口;最底层的驱动可以实现对用户透明的硬件控制。RainBuilder工具链使用简单,部署方AG真人国际便,通用性强,可以让用户快速和低成本的部署和迁移已有算法到CAISA硬件平台上。

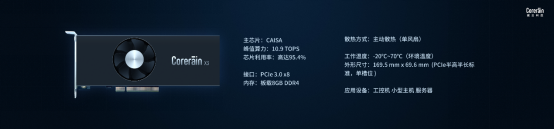

作为全球首款采用数据流技术的AI芯片,CAISA搭载了四个CAISA 3.0引擎,具有超过1.6万个MAC(乘累加)单元,峰值性能可达10.9TOPs。该芯片采用28nm工艺,通过PCIe 3.0×4接口与主处理器通信,同时具有双DDR通道,可为每个CAISA引擎提供超过340Gbps的带宽。

作为一款面向边缘和云端推理的人工智能芯片,CAISA可实现最高95.4%的芯片利用率,为客户提供更高的算力性价比。CAISA芯片具有良好的通用性,可支持所有常用AI算子,通过数据流网络中算子的不同配置和组合,CAISA芯片可支持绝大多数的CNN算法。针对CAISA芯片,鲲云提供RainBuilder 3.0工具链,可实现推理模型在芯片上的端到端部署,使软件工程师可以方便的完成CAISA芯片在AI应用系统中的集成。

另外,鲲云科技还发布了基于CAISA芯片的星空系列边缘和数据中心计算平台,X3加速卡和X9加速卡,并公布了由人工智能产业技术联盟(AIIA)测试的包括ResNet-50, YOLO v3等在内的主流深度学习网络的实测性能。

星空X3加速卡是搭载单颗CAISA 芯片的数据流架构深度学习推断计算平台,为工业级半高半长单槽规格的PCIe板卡。得益于其轻量化的规格特点,X3加速卡可以与不同类型的计算机设备进行适配,包括个人电脑、工业计算机、网络视频录像机、工作站、服务器等,满足边缘和高性能场景中的AI计算需求。相较于英伟达边缘端旗舰产品Xavier,X3可实现1.48-4.12倍的实测性能提升。

星空X9加速卡为搭载4颗CAISA 芯片的深度学习推断板卡,峰值性能43.6TOPS,主要满足高性能场景下的AI计算需求。同英伟达旗舰产品T4相对,X9在ResNet-50, YOLO v3等模型上的芯片利用率提升2.84-11.64倍。在实测性能方面,X9在ResNet50可达5240FPS,与T4性能接近,在YOLO v3、UNet Industrial等检测分割网络,实测性能相较T4有1.83-3.91倍性能提升。在达到最优实测性能下,X9处理延时相比于T4降低1.83-32倍。实测性能以及处理延时的大幅领先,让数据流架构为AI芯片的发展提供了提升峰值性能之外的另一条技术路线。

鲲云科技通过CAISA数据流架构提高芯片利用率,同样的实测性能,对芯片峰值算力的要求可大幅降低3-10倍,从而降低芯片的制造成本,为客户提供更高的算力性价比。目前星空X3加速卡已经实现量产,星空X9加速卡将于今年8月推出市场。(校对/ICE)

意法高层透露与华虹40nmMCU合作细节:专用产线制造 明年底首批产品推出